Article

Upgrade DAQ CMS :

pleine puissance réussie

Upgrade DAQ du détecteur PIXEL de CMS

Le détecteur Pixel de CMS est composé, historiquement et depuis le démarrage de CMS en 2011, de trois couches de détection et d’une électronique de lecture et de contrôle/commande basée sur la technologie VME.

Du fait de la montée continue en puissance du LHC et de l’augmentation programmée de la luminosité du faisceau sur toute sa période d’exploitation, un double problème était attendu à terme pour ce détecteur Pixel, sous-détecteur de CMS le plus proche du point de collision des particules.

D’une part une perte d’efficacité pour les analyses de physique anticipée à l’horizon de fin 2016 due à la dose d’irradiation que les composants ont accumulés et d’autre part l’augmentation de la luminosité du LHC entrainant un accroissement très important du flux d’information extrait de CMS trop conséquent pour la chaine d’acquisition initiale.

La décision a été prise par la collaboration CMS de concevoir un détecteur Pixel de nouvelle génération qui a été mis en place durant l’arrêt hivernal de l’hiver 2016/2017. Ce nouveau détecteur est composé de 4 couches de détection (au lieu de trois précédemment) offrant une meilleure résolution spatiale et capable de supporter l’augmentation de luminosité du LHC. La chaine d’acquisition devant également suivre cette évolution avec une nouvelle architecture matérielle (à forte bande passante au format xTCA) et logicielle.

Projet upgrade DAQ

En Janvier 2013, forte de son expérience dans la conception de prototypes de DAQ xTCA acquise dans le cadre des upgrades Phase 2 de CMS, l’équipe SMA de l’IPHC a été sollicitée par le CERN pour assurer tant la coordination technique que l’essentiel des spécifications et des développements firmware et software bas niveau de la DAQ xTCA devant être rattachée au futur détecteur Pixel.

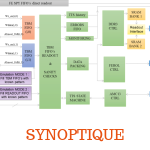

Ces développements ont été réalisés de façon conjointe avec le CERN fournissant les cartes électroniques formant la nouvelle architecture à l’IPHC en charge du développement de la nouvelle DAQ et contrôle et commande du nouveau détecteur pixel. Vous trouverez ci-dessous le synoptique des fonctions de la DAQ, la composante PixFED (acquisition de données) et la composante TkFEC (contrôle et commande).

|

|

|

Détails technique de la composante PixFED (acquisition)

Basée sur un FPGA de la famille Kintex 7, la carte d’acquisition de données (i.e. PixFED) présente, de façon extrêmement résumée, les spécifications suivantes :

24 fibres optiques en entrée (=48 canaux, 2 canaux TBM par fibre) par PixFED, chaque fibre assurant la lecture d’un groupe de modules Pixel via un lien série 400Mb/s connecté, côté détecteur, à un chip TBM (Token Bit Manager).

Ces 24 fibres sont connectées, en deux groupes de 12, à une unique FMC conçue explicitement pour les besoins d’exploitation du détecteur Pixel (une FMC par FC7) ; chaque FMC est équipée de deux opto-récepteurs Fitel Rx (1 faisceau de 12 fibres par opto- récepteur Fitel Rx)

Les FMCs utilisées offrent une interface de sortie 10Gbits Ethernet, exploitant un format de données propriétaire (CERN/Central-DAQ)

Détails technique de la composante TkFEC (contrôle et commande)

Le système de contrôle/commande du détecteur Pixel (TrackerFEC), basé sur cette même carte FC7, implémente sur un support μTCA une réplication à l’identique des fonctions FEC historiquement implémentées sur cartes VME 9U.

Cette rétro-compatibilité a été voulue et pensée pour que l’intégralité des suites logicielles de contrôle/commande et de Run Control de haut niveau puissent être utilisées indifféremment tant sur une ancienne version d’architecture (VME que sur une nouvelle (uTCA), et cela de façon totalement transparente pour les utilisateurs.

Le nouveau détecteur Pixel opérationnel à pleine puissance

Durant l’arrêt hivernal étendu (EYETS) 2016/2017, le nouveau détecteur Pixel a été inséré dans CMS en remplacement de l’ancien et le système de DAQ et de contrôle/commande a été connecté aux mécanismes de supervision et de pilotage centralisés de CMS.

Le premier mai 2017, les premières collisions de redémarrage LHC ont eu lieu sous forme de trains de 10 paquets de protons. Le 26 juin 2017, les valeurs nominales LHC ciblées pour la période 2017 – 2018 ont été atteintes, soit des trains de 2460 paquets de protons fournissant une luminosité instantanée de 1.45e34 et un pileUp de 45.

Durant toute la phase de montée en luminosité du LHC après son redémarrage, les systèmes de DAQ et de contrôle/commande uTCA ont fonctionné en mode nominal, ne causant ni blocage ni ralentissement de CMS durant cett phase de commissionning. Les données issues du nouveau détecteur Pixel acquises en production ont été validées (Data Quality : Good), tant pour celles acquises durant la phase de redémarrage que pour celles acquises une fois le mode de fonctionnement nominal du LHC atteint.

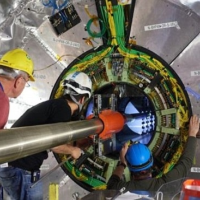

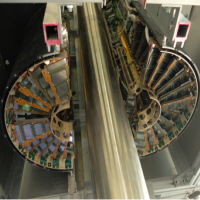

Quelques photos (©CERN) du nouveau détecteur Pixel et son intégration dans l’expérience CMS autour du tube faisceau:

|

|

|

|

Contact: Laurent Charles (IPHC), Laurent Gross (IPHC)