Article

FEERIC : un succès pour ALICE

FEERIC : un succès pour ALICE

FEERIC : un succès pour ALICE

L’expérience ALICE est dédiée à l’étude des propriétés du plasma de quarks-gluons. Le spectromètre à muons contribue à ces études par la mesure de la production de muons dans les collisions d’ions lourds, ainsi qu’en collisions p‑p et p‑A.

Le déclencheur (Muon Trigger) du spectromètre à muons permet de sélectionner les événements d’intérêt, contenant au moins un muon.

L’architecture électronique du détecteur ALICE fait l’objet d’un ambitieux programme de mise à niveau prévoyant la lecture de toutes les collisions et le traitement en ligne des données. Dans ce cadre, le déclencheur change de fonction, et donc de nom, pour devenir l’identificateur de muons (MID : Muon IDentifier).

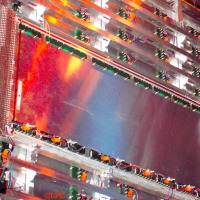

Cette amélioration prévoit un remplacement de l’électronique frontale et de lecture de MID, en vue de supporter l’augmentation de luminosité du LHC prévue après 2020. En effet, les chambres à plaques résistives (RPC : Resistive Plate Chambers) vont être exposées à des flux de particules jusqu’à 100 collisions/s/cm2. Afin de limiter les effets de vieillissement des RPC, il est prévu de réduire le gain du détecteur (en réduisant la haute tension de polarisation), ce qui implique de remplacer l’électronique frontale actuelle par des circuits amplifiés.

Le circuit FEERIC (Front-End Electronics Rapid Integrated Circuit) a été conçu pour répondre à ce besoin.

Vidéo présentant l’expérience ALICE au CERN]

Descriptif du circuit FEERIC

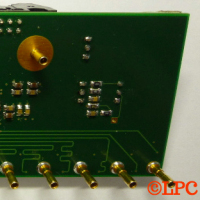

L’électronique frontale des chambres de MID représente 20 992 voies, soit 2 720 cartes connectées aux pistes de lecture des RPC.

L’électronique frontale des chambres de MID représente 20 992 voies, soit 2 720 cartes connectées aux pistes de lecture des RPC.

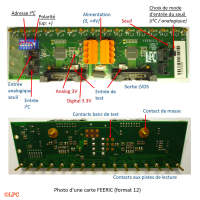

Les cartes se déclinent en six formats différents selon la segmentation des pistes de lecture (environ 1 cm de largeur près de l’axe du faisceau et 4 cm en périphérie).

Le rôle de l’électronique frontale est de produire des signaux logiques en réponse aux impulsions induites sur les pistes de lecture des RPC. Ces pistes sont orientées dans une direction X sur une face des RPC et dans la direction orthogonale Y sur l’autre face. Les cartes frontales sont connectées à une extrémité des pistes, l’autre extrémité étant terminée par une résistance (50 Ω).

La lecture sur les deux faces impose au circuit FEERIC d’être compatible avec des impulsions positives ou négatives en entrée.

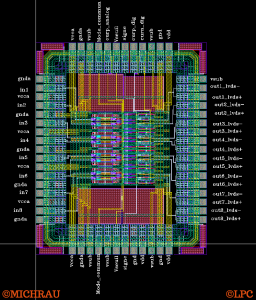

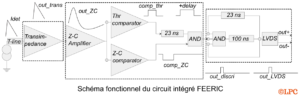

FEERIC est un ASIC 8 voies conçu en technologie AMS CMOS 0,35 µm. Il est composé d’un étage amplificateur à transimpédance, un discriminateur à zero-crossing et un système dit de “one shot” qui empêche le redéclenchement pendant 100 ns. Le seuil de fonctionnement visé est compris entre 60 et 100 fC.

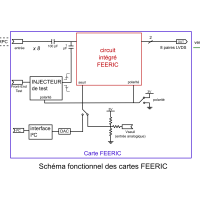

L’image ci-dessous présente le schéma fonctionnel du circuit intégré FEERIC

Descriptif des cartes intégrant les circuits FEERIC

Les cartes électroniques intégrant les circuits FEERIC ont été produites à plus de 2 384 cartes, le schéma fonctionnel ci-contre de la carte FEERIC permet de comprendre l’architecture du circuit intégré.

Une présérie de 39 cartes a été installée sur une RPC début 2015 dans la caverne d’ALICE, et des résultats satisfaisants ont été enregistrés depuis. La réduction du gain de la RPC a permis de réduire d’un facteur 4 le courant dans le gaz. L’efficacité est supérieure à > 95 % (typiquement 98 %) avec une bonne stabilité dans le temps, ce qui répond à l’objectif initial d’un facteur 3 à 5 pour ralentir le vieillissement des RPC.

|

|

|

Banc de tests et résultats des mesures

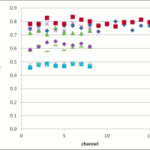

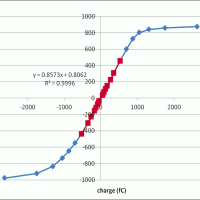

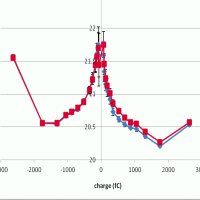

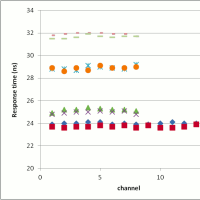

Le banc de tests permettant la validation finale de la production a été conçu au Laboratoire de physique de Clermont (LPC, CNRS/Université Clermont Auvergne) par Frédéric Jouve et a été fourni à la société en charge de la fabrication. Les principaux résultats de mesures (ci-dessous) montrent les caractéristiques finales des circuits FEERIC sur l’ensemble des puces produites avec leur reproductibilité pour ce qui est des gains, des seuils, du temps de réponse des circuits et des cartes. En effet, de même que le gain, le temps de réponse varie en fonction de l’impédance des pistes de lecture, mais reste bien constant entre voies pour un format donné. Ces différences seront compensées par intervalles de 3 ns au niveau des cartes de readout recevant les signaux logiques de FEERIC.

Le banc de tests permettant la validation finale de la production a été conçu au Laboratoire de physique de Clermont (LPC, CNRS/Université Clermont Auvergne) par Frédéric Jouve et a été fourni à la société en charge de la fabrication. Les principaux résultats de mesures (ci-dessous) montrent les caractéristiques finales des circuits FEERIC sur l’ensemble des puces produites avec leur reproductibilité pour ce qui est des gains, des seuils, du temps de réponse des circuits et des cartes. En effet, de même que le gain, le temps de réponse varie en fonction de l’impédance des pistes de lecture, mais reste bien constant entre voies pour un format donné. Ces différences seront compensées par intervalles de 3 ns au niveau des cartes de readout recevant les signaux logiques de FEERIC.

|

|

|

|

Rappels sur production des cartes ainsi que intégration dans le détecteur ALICE

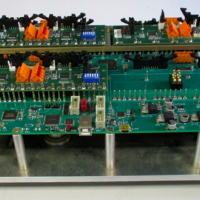

La production des ASICs a été livrée en avril 2016. Tous les circuits ont été testés à l’aide d’un banc de test développé au LPC. Le rendement s’élève à 98 %.

A l’issue d’une procédure de marché public, la production des 2 720 cartes FEERIC (rechanges incluses) s’est déroulée du printemps 2017 à janvier 2018. Toutes les cartes ont été testées par la firme au moyen du banc de test fourni par le LPC, et des tests complémentaires par échantillonnage ont été effectués au LPC.

L’installation, prévue en 2019, est en cours de préparation en vue de l’intégration finale dans l’expérience ALICE et clos avec succès le développement de ce circuit intégré FEERIC.

Les personnes suivantes ont contribué de manière significative aux développements techniques pour l’électronique frontale du MID, sous la responsabilité scientifique de Pascal Dupieux :

- Samuel Manen, Richard Vandaële (ASIC)

- Baptiste Joly, Marie-Lise Mercier (cartes)

- Frédéric Jouve (banc de test de production)

- Christian Fayard, Martine Bony : câblage, outils de test et test de pré-série

Photo de l’équipe avec de gauche à droite Pascal Dupieux, Richard Vandaële, Martine Bony, Samuel Manen, Christophe INSA, Frédéric Jouve, Baptiste Joly, Christian Fayard, Marie-Lise Mercier